香港中文大學

The Chinese University of Hong Kong

#### CENG3430 Rapid Prototyping of Digital Systems Lecture 04: Combinational Circuit and Sequential Circuit

## Ming-Chang YANG

mcyang@cse.cuhk.edu.hk

#### Outline

- Combinational Circuit and Sequential Circuit

- Combinational Circuit: No Memory

- Decoder

- Multiplexer

- Bi-directional Bus

- Sequential Circuit: Has Memory

- Latch

- Flip-flop

- Asynchronous Reset and Synchronous Reset

- Finite State Machine (FSM)

- Clock Edge Detection

- Direct Feedback Path

- Types and Examples

## **Combinational Circuit**

- Combinational Circuit: no memory

- Outputs are a function of the present inputs only.

- As soon as inputs change, the values of previous outputs are lost.

- It has no internal state (i.e., has no memory).

- Common Examples: Comparator, Encoder/Decoder, Full/Half Adder, Multiplexer, Bi-directional Bus, etc.

- Rule: You can build a combinational circuit using <u>either</u> concurrent statements (i.e., statements outside process)

or sequential statements (i.e., statements inside process).

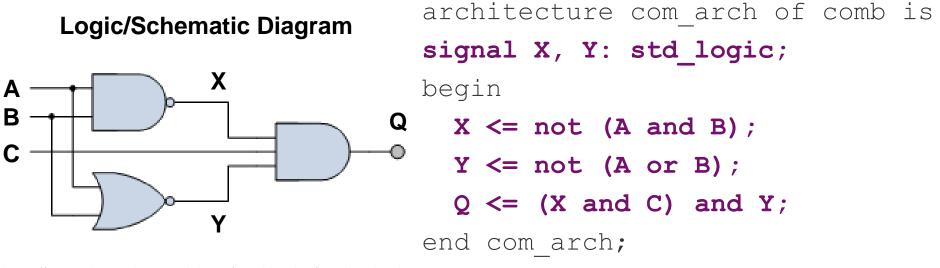

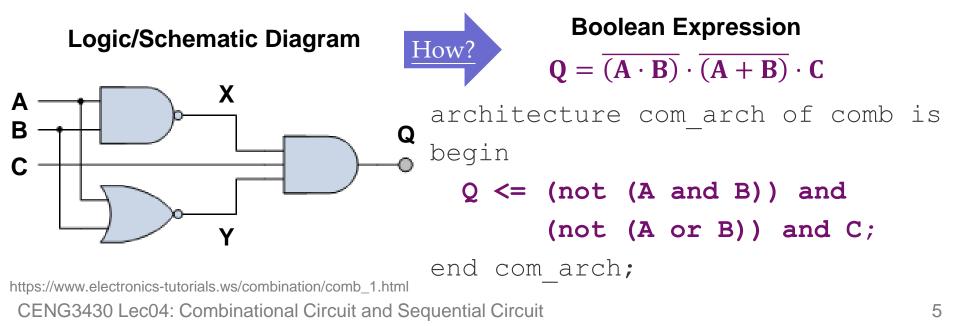

## Modeling Combinational Logic (1/3)

- Three typical ways for modeling a combinational logic:

- 1) Logic/Schematic Diagram shows the wiring and connections of each individual logic gate.

- 2) Boolean Expression is an expression in Boolean algebra that represents the logic circuit.

- **3) Truth Table** provides a concise list that shows all the output states for each possible combination of inputs

https://www.electronics-tutorials.ws/combination/comb\_1.html

## Modeling Combinational Logic (2/3)

- Three typical ways for modeling a combinational logic:

- 1) Logic/Schematic Diagram shows the wiring and connections of each individual logic gate.

- 2) Boolean Expression is an expression in Boolean algebra that represents the logic circuit.

- 3) Truth Table provides a concise list that shows all the output states for each possible combination of inputs

## Modeling Combinational Logic (3/3)

- Three typical ways for modeling a combinational logic:

- 1) Logic/Schematic Diagram shows the wiring and connections of each individual logic gate.

- 2) Boolean Expression is an expression in Boolean algebra that represents the logic circuit.

- **3) Truth Table** provides a concise list that shows all the output states for each possible combination of inputs

| Α                                                                 | B | С | Q | process (A, B, C)                                 |  |

|-------------------------------------------------------------------|---|---|---|---------------------------------------------------|--|

| 0                                                                 | 0 | 0 | 0 | begin                                             |  |

| 0                                                                 | 0 | 1 | 1 | if ( $A = '0'$ and $B = '0'$ and $C = '1'$ ) then |  |

| 0                                                                 | 1 | 0 | 0 | Q <= '1';                                         |  |

| 0                                                                 | 1 | 1 | 0 |                                                   |  |

| 1                                                                 | 0 | 0 | 0 | else                                              |  |

| 1                                                                 | 0 | 1 | 0 | Q <= '0';                                         |  |

| 1                                                                 | 1 | 0 | 0 | <pre>end if;</pre>                                |  |

| 1                                                                 | 1 | 1 | 0 | end process;                                      |  |

| CENICO 400 Les 0.4. Compliantianal Circuit and Convential Circuit |   |   |   |                                                   |  |

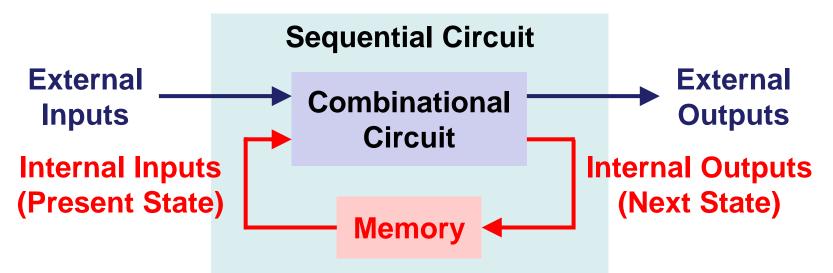

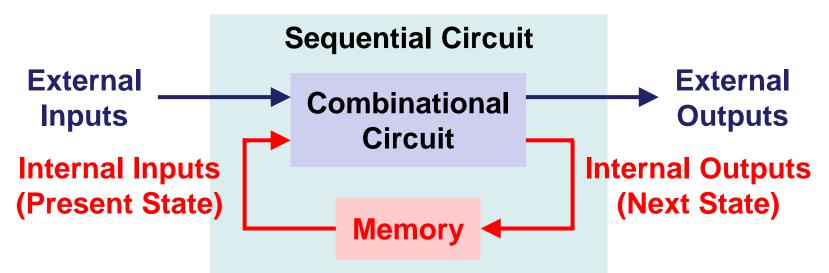

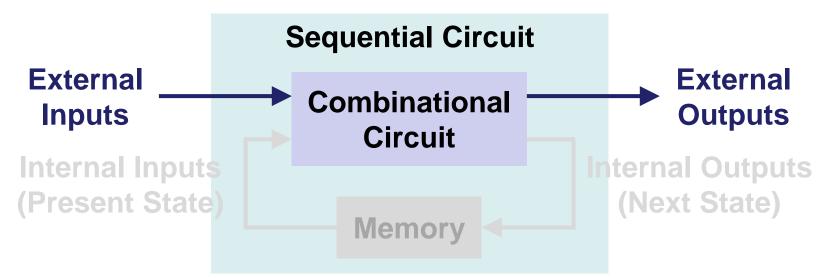

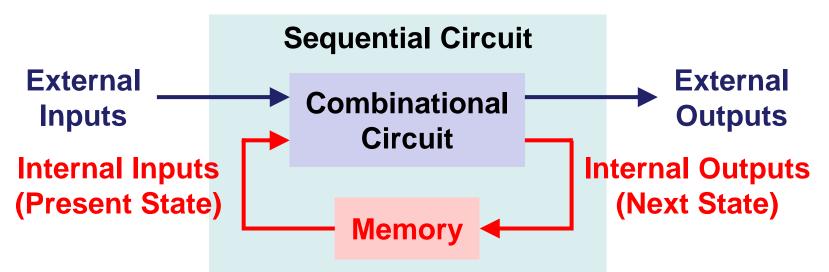

#### **Sequential Circuit**

- Sequential Circuit: has memory

- Outputs are a function of <u>the present inputs</u> and <u>the</u> <u>previous</u> outputs (i.e., the **internal state**).

- It changes outputs based on <u>inputs</u>; but the outputs also depend upon <u>previous outputs</u> (i.e., the **internal state**) (i.e., has memory).

- Example: Latch, Flip-Flop, Finite State Machine, etc.

- Rule: You must build a sequential circuit with <u>only</u>

<u>sequential statements</u> (i.e., statements inside process).

#### **Combinational vs. Sequential Circuit**

#### Combinational Circuit: no memory

- ① Outputs are a function of the *present* inputs only.

- ② Rule: Use either concurrent or sequential statements.

- Sequential Circuit: has memory

- ① Outputs are a function of <u>the present inputs</u> and <u>the previous outputs</u> (i.e., the **internal state**).

- ② Rule: Must use sequential statements (i.e., process).

#### Outline

- Combinational Circuit and Sequential Circuit

- Combinational Circuit: No Memory

- Decoder

- Multiplexer

- Bi-directional Bus

- Sequential Circuit: Has Memory

- Latch

- Flip-flop

- Asynchronous Reset and Synchronous Reset

- Finite State Machine (FSM)

- Clock Edge Detection

- Direct Feedback Path

- Types and Examples

#### **Recall: Combinational Circuit**

- Combinational Circuit: no memory

- ① Outputs are a function of the *present* inputs only.

- ② Rule: Use either concurrent or sequential statements.

- Sequential Circuit: has memory

- ① Outputs are a function of <u>the present inputs</u> and <u>the</u> <u>previous</u> outputs (i.e., the **internal state**).

- ② Rule: Must use sequential statements (i.e., process).

#### **Combinational Logic as a Process**

• Consider a simple combinational logic:

$c \ll a$  and b;

• This logic can be also modeled as a process:

- All signals referenced in process must be in sensitivity list. entity And Good is

port (a, b: in std\_logic; c: out std\_logic); end And\_Good; architecture Synthesis Good of And Good is

begin

process (a, b) -- sensitive to signals a and/or b

begin

c <= a and b; -- c updated

#### end process;

end;

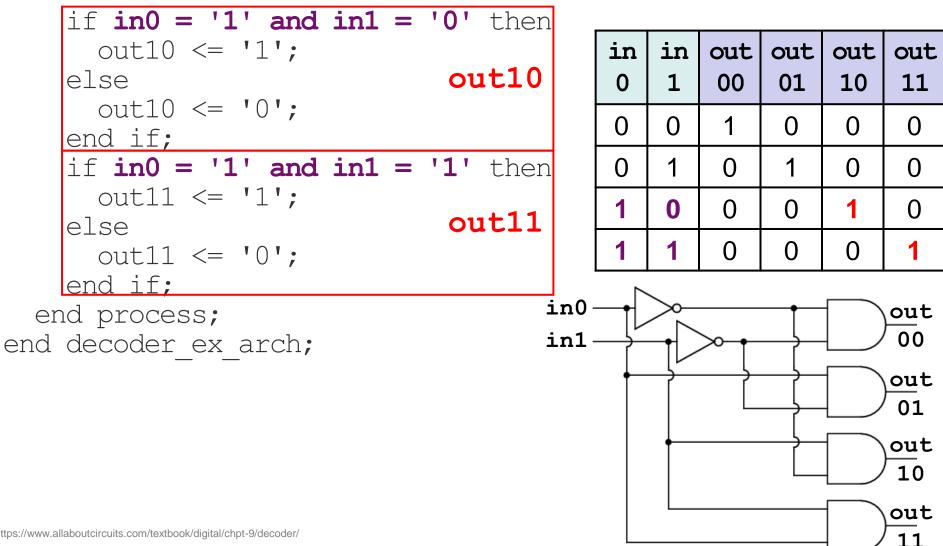

#### **Combinational Circuit: Decoder (1/2)**

```

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

entity decoder_ex is

port (in0,in1: in std_logic;

out00,out01,out10,out11: out std_logic);

end decoder_ex;

architecture decoder_ex_arch of decoder_ex is

begin

```

```

process (in0, in1)

```

begin

| if in0 = '0' and in1 = | <b>= '0'</b> then   |

|------------------------|---------------------|

| out00 <= '1';          |                     |

| else                   | out00               |

| out00 <= '0';          |                     |

| end if;                |                     |

| if in0 = '0' and in1 = | = ' <b>1</b> ' then |

| out01 <= '1';          |                     |

| else                   | out01               |

| out01 <= '0';          |                     |

| end if;                |                     |

| in<br>0 | in<br>1 | out<br>00 | out<br>01 | out<br>10 | out<br>11 |

|---------|---------|-----------|-----------|-----------|-----------|

| 0       | 0       | 1         | 0         | 0         | 0         |

| 0       | 1       | 0         | 1         | 0         | 0         |

| 1       | 0       | 0         | 0         | 1         | 0         |

| 1       | 1       | 0         | 0         | 0         | 1         |

#### **Combinational Circuit: Decoder (2/2)**

13

https://www.allaboutcircuits.com/textbook/digital/chpt-9/decoder/

#### **Class Exercise 4.1**

| Student ID: |  |

|-------------|--|

| Name:       |  |

Date:

);

• Implement the Encoder based on the given table: port (

... architecture encoder\_ex\_arch of encoder\_ex is begin process ( ) begin

| end process;                                                                          |  |

|---------------------------------------------------------------------------------------|--|

| end encoder ex arch •<br>CENG3430 Lec04: Combinational Circuit and Sequential Circuit |  |

| in | in | in | in | out | out |

|----|----|----|----|-----|-----|

| 00 | 01 | 10 | 11 | 0   | 1   |

| 1  | 0  | 0  | 0  | 0   | 0   |

| 0  | 1  | 0  | 0  | 0   | 1   |

| 0  | 0  | 1  | 0  | 1   | 0   |

| 0  | 0  | 0  | 1  | 1   | 1   |

#### Outline

- Combinational Circuit and Sequential Circuit

- Combinational Circuit: No Memory

- Decoder

- Multiplexer

- Bi-directional Bus

- Sequential Circuit: Has Memory

- Latch

- Flip-flop

- Asynchronous Reset and Synchronous Reset

- Finite State Machine (FSM)

- Clock Edge Detection

- Direct Feedback Path

- Types and Examples

#### **Combinational Circuit: Multiplexer**

```

library IEEE;

use IEEE.STD LOGIC 1164.ALL;

entity mux ex is

port (in1, in2, sel: in std logic;

out1: out std logic);

end mux ex;

architecture mux ex arch of mux ex is

begin

process (in1, in2, sel)

begin

if sel = '0' then

out1 <= in1; -- select in1</pre>

else

out1 <= in2; -- select in2

end if;

end process;

end mux ex arch;

```

CENG3430 Lec04: Combinational Circuit and Sequential Circuit

?

MUX

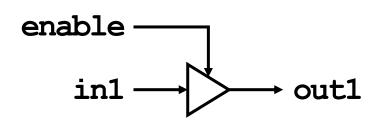

#### **Recall: Tri-state Buffer**

| in1 | enable | out1 |

|-----|--------|------|

| 0   | 0      | Z    |

| 1   | 0      | Z    |

| 0   | 1      | 0    |

| 1   | 1      | 1    |

## outl <= inl when enable = '1' else 'Z'; end tri\_ex\_arch; CENG3430 Lec04: Combinational Circuit and Sequential Circuit</pre>

#### **Class Exercise 4.2**

| Student ID: | Date: |

|-------------|-------|

| Name:       | <br>  |

Specify the I/O signals in the circuit:

```

entity mux ex is

port (in1, in2, sel: in std logic;

out1: out std logic);

end mux ex;

architecture mux ex arch of mux ex is

begin

process (in1, in2, sel)

begin

if sel = '0' then

out1 <= in1;</pre>

else

out1 \leq in2;

MUX

end if;

end process;

end mux ex arch;

```

#### Outline

- Combinational Circuit and Sequential Circuit

- Combinational Circuit: No Memory

- Decoder

- Multiplexer

- Bi-directional Bus

- Sequential Circuit: Has Memory

- Latch

- Flip-flop

- Asynchronous Reset and Synchronous Reset

- Finite State Machine (FSM)

- Clock Edge Detection

- Direct Feedback Path

- Types and Examples

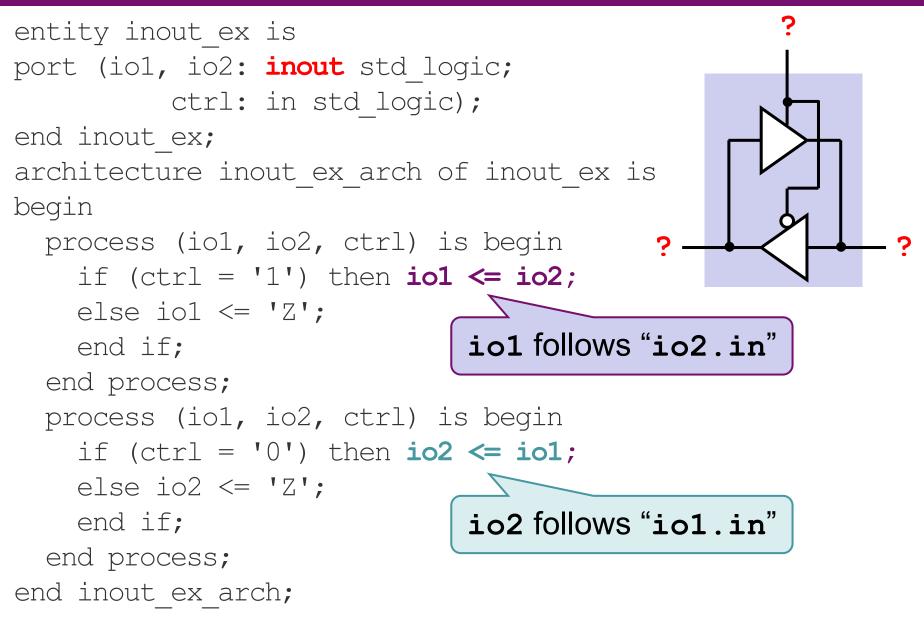

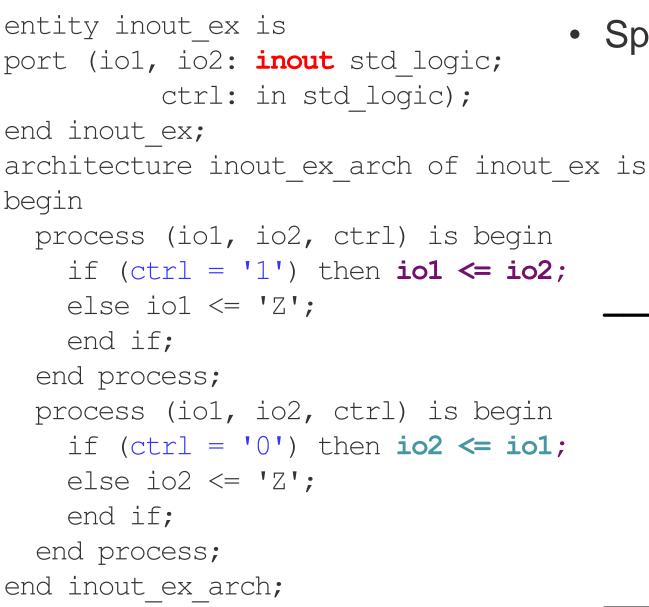

#### **Combinational Circuit: Bi-directional Bus**

#### **Class Exercise 4.3**

CENG3430 Lec04: Combinational Circuit and Sequential Circuit

• Specify I/O signals:

Date:

Student ID: \_\_\_\_

Name:

#### Outline

#### Combinational Circuit and Sequential Circuit

- Combinational Circuit: No Memory

- Decoder

- Multiplexer

- Bi-directional Bus

- Sequential Circuit: Has Memory

- Latch

- Flip-flop

- Asynchronous Reset and Synchronous Reset

- Finite State Machine (FSM)

- Clock Edge Detection

- Direct Feedback Path

- Types and Examples

## **Recall: Sequential Circuit**

- Combinational Circuit: no memory

- ① Outputs are a function of the present inputs only.

2 **Rule**: Use **either** concurrent **or** sequential statements.

- Sequential Circuit: has memory

- Outputs are a function of <u>the present inputs</u> and <u>the</u> <u>previous</u> outputs (i.e., the **internal state**).

- ② Rule: Must use sequential statements (i.e., process).

#### **Latches and Flip Flops**

- Latches and Flip-flops (FF) are the basic elements used to store information.

- Each latch and flip flop can keep one bit of data.

- The main difference between latch and flip-flop:

- A latch continuously checks input and changes the output whenever there is a change in input.

- A latch has **no** clock signal.

- A flip-flop continuously checks input and changes the output only at times determined by the clock signal.

- A flip flop has a clock signal.

#### Outline

#### Combinational Circuit and Sequential Circuit

- Combinational Circuit: No Memory

- Decoder

- Multiplexer

- Bi-directional Bus

- Sequential Circuit: Has Memory

- Latch

- Flip-flop

- Asynchronous Reset and Synchronous Reset

- Finite State Machine (FSM)

- Clock Edge Detection

- Direct Feedback Path

- Types and Examples

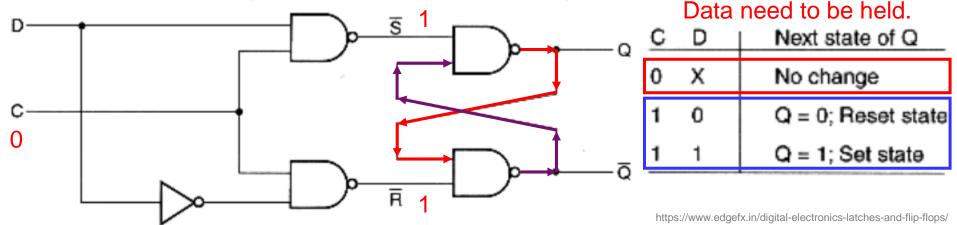

#### Sequential Circuit: Latch (1/2)

- Latches are asynchronous (no CLOCK signal).

- It changes output only in response to input.

- Case Study: D Latch

- When enable line C is high, the output Q follows input D.

- $\rightarrow$  That is why D latch is also called as transparent latch.

- When enable line C is asserted, the latch is said to be transparent.

- When C falls, the last state of D input is trapped and held.

- $\rightarrow$  That is why the latch has memory!

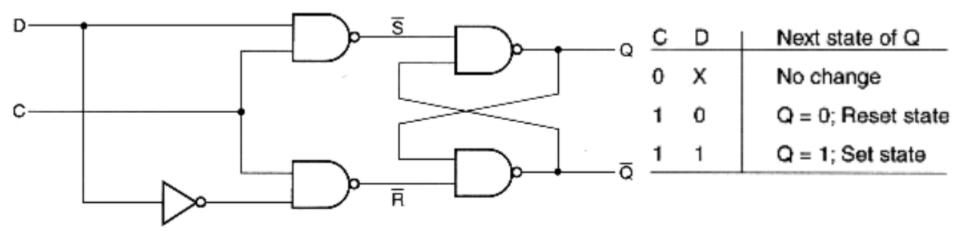

## Sequential Circuit: Latch (2/2)

| 2<br>3 | use<br>enti                                 | rary IEEE;(ok vivado 2014<br>IEEE.STD_LOGIC_1164.ALL;<br>ity latch_ex is | .4) | $\rightarrow$ D Q $\rightarrow$                                   |  |  |

|--------|---------------------------------------------|--------------------------------------------------------------------------|-----|-------------------------------------------------------------------|--|--|

| 4      | port                                        | t (C, D: in std_logic;                                                   |     | $\rightarrow$ C                                                   |  |  |

| 5      |                                             | Q: out std_logic);                                                       |     |                                                                   |  |  |

| 6      | end                                         | latch_ex;                                                                |     |                                                                   |  |  |

| 7      | 7 architecture latch ex arch of latch ex is |                                                                          |     |                                                                   |  |  |

| 8      | begi                                        | in                                                                       |     |                                                                   |  |  |

| 9      | pı                                          | rocess(C, D) sensitivity                                                 | lis | t                                                                 |  |  |

| 10     | be                                          | egin                                                                     | -   |                                                                   |  |  |

| 11     |                                             | if $(C = '1')$ then $\underline{C}$                                      | 0   | Next state of Q                                                   |  |  |

| 12     |                                             | Q <= D;                                                                  | Х   | No change                                                         |  |  |

| 13     |                                             | end if;                                                                  | 0   | Q = 0; Reset state                                                |  |  |

|        |                                             | no change (memory)                                                       | -   |                                                                   |  |  |

| 14     | er                                          | nd process;                                                              | 1   | Q = 1; Set state                                                  |  |  |

| 15     | end                                         | latch_ex_arch;                                                           |     | https://www.edgefx.in/digital-electronics-latches-and-flip-flops/ |  |  |

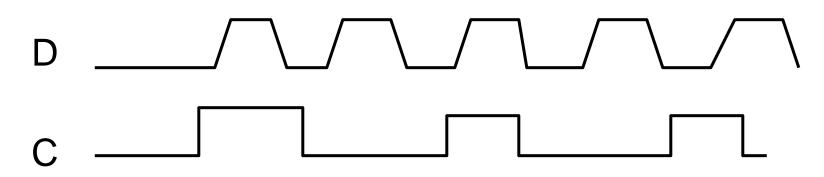

#### **Class Exercise 4.4**

| Student ID: |  |

|-------------|--|

| Name:       |  |

• Given a D latch, draw Q in the following figure:

Q

CENG3430 Lec04: Combinational Circuit and Sequential Circuit

Date:

#### Outline

#### Combinational Circuit and Sequential Circuit

- Combinational Circuit: No Memory

- Decoder

- Multiplexer

- Bi-directional Bus

- Sequential Circuit: Has Memory

- Latch

- Flip-flop

- Asynchronous Reset and Synchronous Reset

- Finite State Machine (FSM)

- Clock Edge Detection

- Direct Feedback Path

- Types and Examples

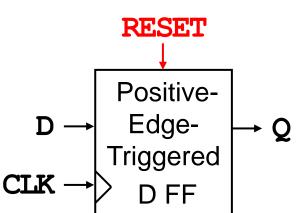

## Sequential Circuit: Flip-flop

- A Latch is a non-clock-controlled memory device.

- ① It has **no** CLOCK signal.

- ② It changes output only in response to <u>data input</u> (i.e., the value is set asynchronously).

- A Flip-flop (FF) is a clock-controlled memory device.

- ① Different from a Latch, it has a <u>CLOCK signal</u> as input.

- ② It stores the input value (i.e., low or high) and outputs the stored value only in response to the <u>CLOCK signal</u>.

- Positive-Edge-Triggered: At every low to high of CLOCK.

- Negative-Edge-Triggered: At every high to low of CLOCK.

- ③ The value can be **reset** asynchronously or synchronously.

- Async. Reset: Reset the value anytime.

- Sync. Reset: Reset the value on positive or negative clock edges.

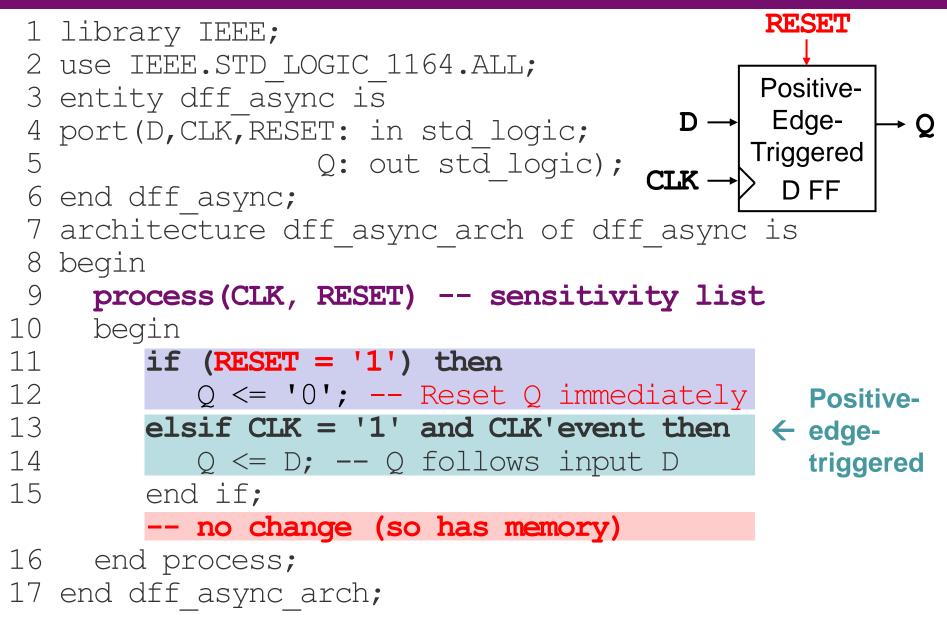

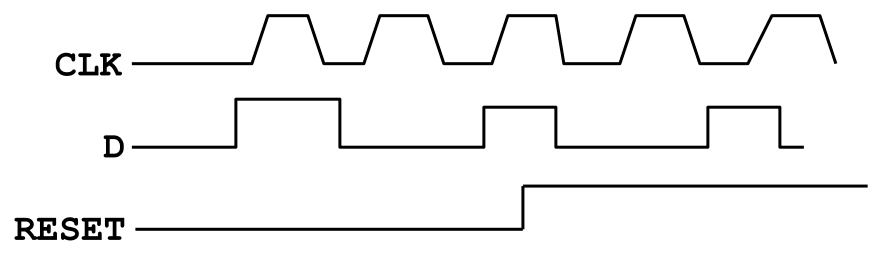

#### Positive-Edge-Triggered FF with Async. Reset

#### **Recall: Attributes (Lec01)**

- Another important signal attribute is the 'event.

- This attribute yields a Boolean value of TRUE <u>if an event</u> has just occurred on the signal.

- It is used primarily to determine if a clock has transitioned.

- Example (*more in Lec04*):

• • •

...

# if clock = '1' and clock'event then my\_out <= my\_in;</pre>

#### **Class Exercise 4.5**

| Student ID: |  |

|-------------|--|

| Name:       |  |

Date:

• Consider the following VHDL implementation of a positive-edge-triggered FF with asynchronous reset:

```

9

process (CLK, RESET) -- sensitivity list

begin

10

if (RESET = '1') then

11

Q <= '0'; -- Reset Q

12

elsif CLK = '1' and CLK' event then

13

14

Q \leq D; --Q follows input D

end if;

15

-- no change (so has memory)

16

end process;

– When will line 9 be executed?

Answer:

```

– Which signal is more "powerful"? CLK or RESET? Answer:

#### CENG3430 Lec04: Combinational Circuit and Sequential Circuit

Q

#### **Class Exercise 4.6** Name: Given a Positive-edge-triggered D Flip-flop with async. reset, draw the output Q. CLK

Student ID: \_\_\_\_\_

Date:

O

RESET

Positive-

Edge-Triggered

D FF

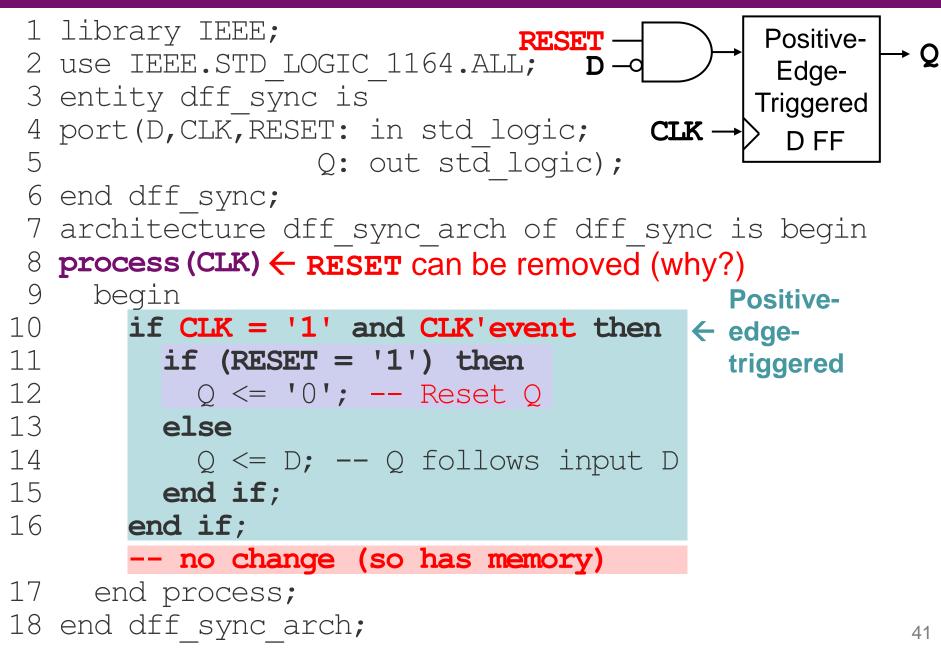

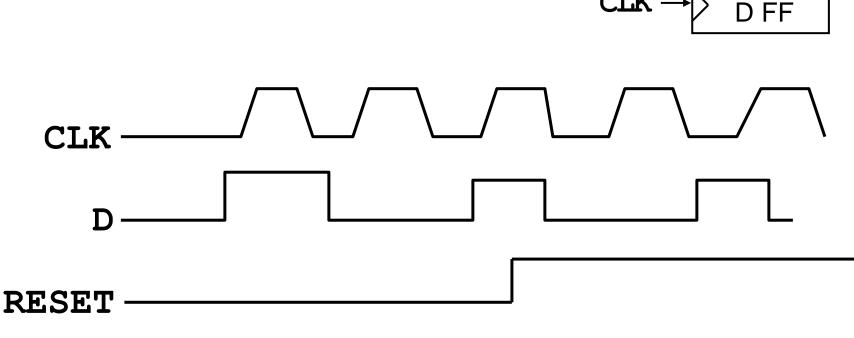

#### Positive-Edge-Triggered FF with Sync. Reset

#### CENG3430 Lec04: Combinational Circuit and Sequential Circuit

Q

#### d Sequential Circuit

Name:

Given a Positive-edge-triggered D Flip-flop with sync. reset, draw the output Q.

#### **Class Exercise 4.7**

# Async. Reset vs. Sync. Reset (1/2)

• The order of the statements inside the process determines asynchronous reset or synchronous reset.

– Asynchronous Reset (check RESET first!)

11 if (RESET = '1') then

12 Q <= '0'; -- Reset Q

13 elsif CLK = '1' and CLK'event then

14 Q <= D; -- Q follows input D

15 end if;</pre>

– Synchronous Reset (check CLK first!)

| 10 | if CLK = '1' and CLK'event then |

|----|---------------------------------|

| 11 | if (RESET = $'1'$ ) then        |

| 12 | Q <= '0'; Reset Q               |

| 13 | else                            |

| 14 | Q <= D; Q follows input D       |

| 15 | end if;                         |

| 16 | end if;                         |

#### Async. Reset vs. Sync. Reset (2/2)

#### Outline

#### Combinational Circuit and Sequential Circuit

- Combinational Circuit: No Memory

- Decoder

- Multiplexer

- Bi-directional Bus

- Sequential Circuit: Has Memory

- Latch

- Flip-flop

- Asynchronous Reset and Synchronous Reset

- Finite State Machine (FSM)

- Clock Edge Detection

- Direct Feedback Path

- Types and Examples

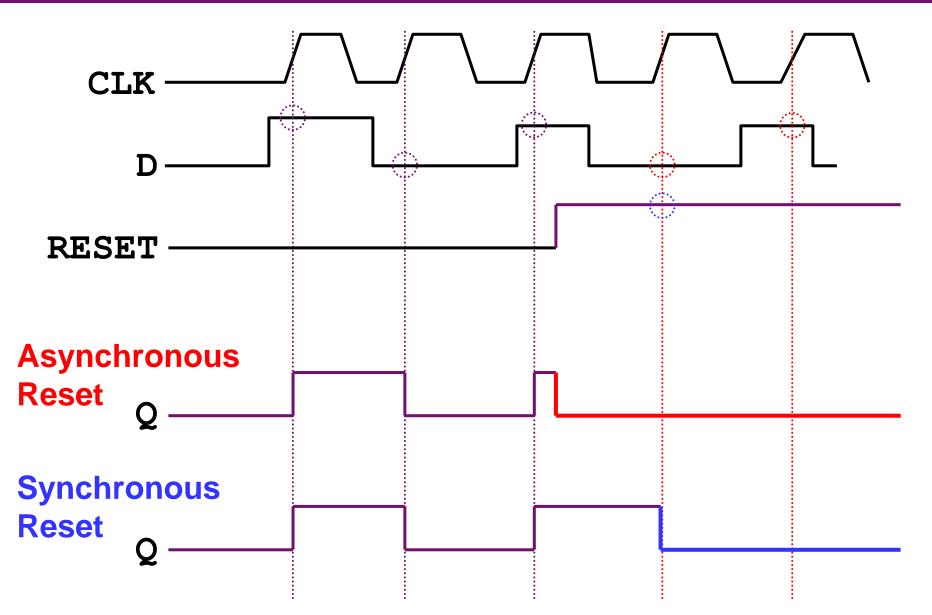

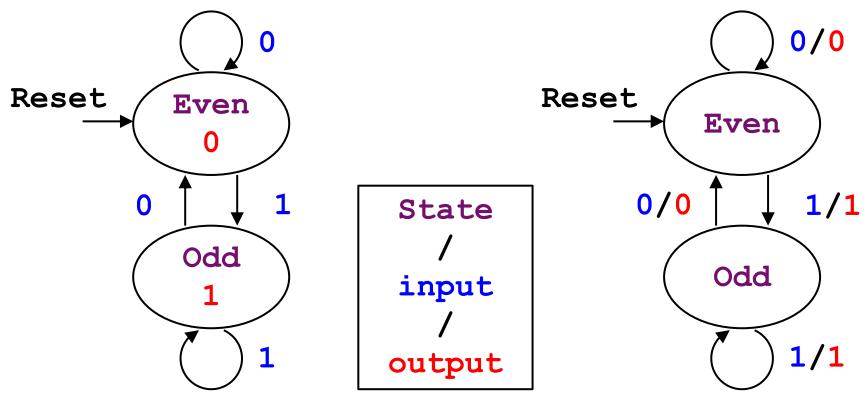

## Finite State Machine (FSM)

- Finite State Machine (FSM): A system jumps from one state to another:

- Within a pool of finite states, and

- Upon clock edges and/or input transitions.

- Example of FSM: traffic light, digital watch, CPU, etc.

• Two crucial factors: *time* (*clock edge*) and *state* (*feedback*)

#### Outline

#### Combinational Circuit and Sequential Circuit

- Combinational Circuit: No Memory

- Decoder

- Multiplexer

- Bi-directional Bus

- Sequential Circuit: Has Memory

- Latch

- Flip-flop

- Asynchronous Reset and Synchronous Reset

- Finite State Machine (FSM)

- Clock Edge Detection

- Direct Feedback Path

- Types and Examples

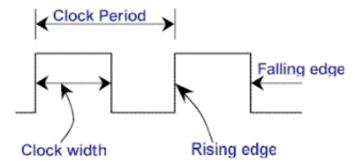

### **Clock Edge Detection**

- Both "wait until" and "if" statements can be used to detect the clock edge (e.g., CLK):

- "wait until" statement:

- wait until CLK = '1'; -- rising edge

- wait until CLK = '0'; -- falling edge

#### • "if" statement:

- if CLK'event and CLK = '1' -- rising edge

- if CLK'event and CLK = '0' -- falling edge

#### OR

- if ( rising\_edge(CLK) ) -- rising edge

- if ( falling\_edge(CLK) ) -- falling edge

#### rising\_edge(CLK) VS. CLK'event

#### rising\_edge() function in std\_logic\_1164 library

FUNCTION rising\_edge (SIGNAL s : std\_ulogic) RETURN BOOLEAN IS

BEGIN

RETURN (s'EVENT AND (To\_X01(s) = '1') AND

(To\_X01(s'LAST\_VALUE) = '0'));

END;

- It results **TRUE** when there is an edge transition in the signal s, the present value is '1' and the last value is '0'.

- If the last value is something like 'z' or 'U', it returns a FALSE.

- The statement (clk'event and clk='1')

- It results **TRUE** when the there is an edge transition in the clk and the present value is '1'.

- It does not see whether the last value is '0' or not.

Use rising\_edge() / falling\_edge() with "if" statements!

#### When to use "wait until" or "if"? (1/2)

- Synchronous Process: Computes values <u>only on</u> <u>clock edges</u> (i.e., only sensitive/sync. to clock signal).

- Rule: Use "wait-until" or "if" for synchronous process: **process**  $\leftarrow$  NO sensitivity list implies that there is one clock signal. begin Usage wait until clk='1'; The *first* statement must be wait until. of "wait until" end process *Note: IEEE VHDL requires that a process with a wait statement must not* have a sensitivity list, and the **first statement** must be **wait until**. **process**  $(clk) \leftarrow$  The clock signal must be in the sensitivity list. begin Usage of **if** ( **rising\_edge**(**clk**) ) ← NOT necessary to be the *first* line. "if"

end process

#### When to use "wait until" or "if"? (2/2)

- Asynchronous Process: Computes values on clock edges or when asynchronous conditions are TRUE.

- That is, it must be sensitive to the <u>clock signal</u> (if any), and to <u>all inputs that may affect the asynchronous behavior</u>.

- Rule: Only use "if" for asynchronous process:

#### Simply use "if" statements for both sync. and async. processes!

#### Outline

#### Combinational Circuit and Sequential Circuit

- Combinational Circuit: No Memory

- Decoder

- Multiplexer

- Bi-directional Bus

- Sequential Circuit: Has Memory

- Latch

- Flip-flop

- Asynchronous Reset and Synchronous Reset

- Finite State Machine (FSM)

- Clock Edge Detection

- Direct Feedback Path

- Types and Examples

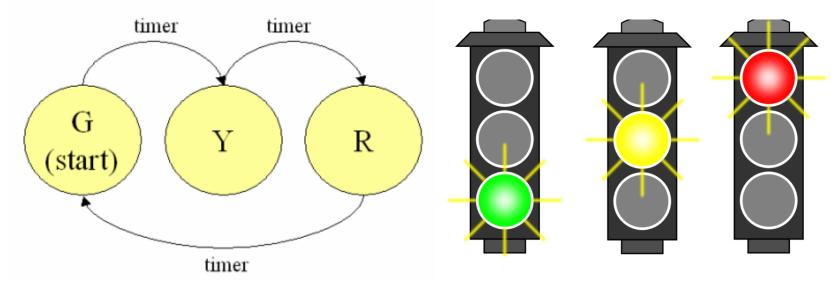

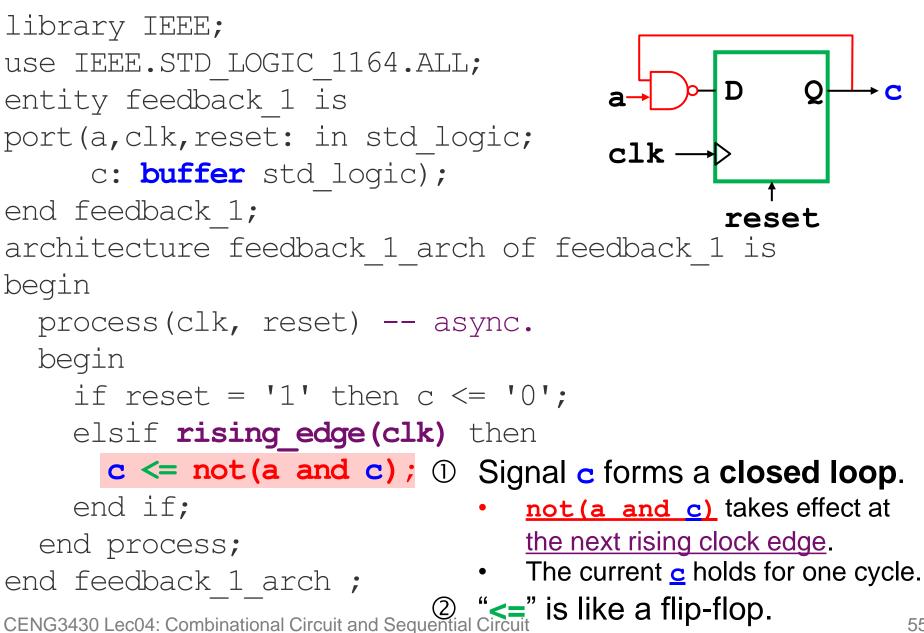

#### **Feed-forward and Feedback Paths**

So far, we mostly focus on logic with feed-forward (or open-loop) paths.

• Now, we are going to learn feedback (or closed-loop) paths—the key step of making a finite state machine.

#### **Direct Feedback Path**

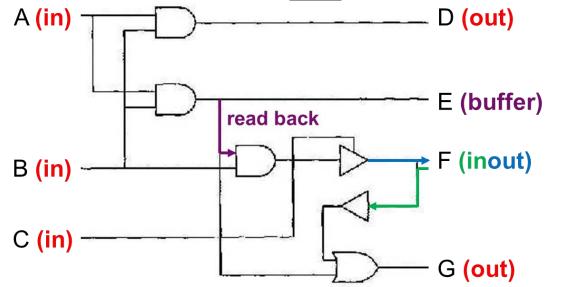

### Internal Feedback: inout or buffer

- Recall (*Lec01*): There are 4 modes of I/O pins:

- 1) in: Data flows in only

- 2) out: Data flows out only (cannot be read back by the entity)

- 3) inout: Data flows **bi-directionally** (i.e., in or out)

- 4) buffer: Similar to out but it can be read back by the entity

- Both buffer and inout can be read back internally.

- inout can also read external input signals.

#### Outline

#### Combinational Circuit and Sequential Circuit

- Combinational Circuit: No Memory

- Decoder

- Multiplexer

- Bi-directional Bus

- Sequential Circuit: Has Memory

- Latch

- Flip-flop

- Asynchronous Reset and Synchronous Reset

- Finite State Machine (FSM)

- Clock Edge Detection

- Direct Feedback Path

- Types and Examples

### **Types of Finite State Machines**

- Moore Machine:

- Outputs are a function of the present state <u>only</u>.

- Mealy Machine:

- Outputs are a function of the present state <u>and</u> the present inputs.

#### Suggestion: Maintain the internal state explicitly!

#### **Moore Machine**

```

Moore Machine: outputs rely on present state only.

architecture moore arch of fsm is

signal s: bit; -- internal state

begin

process (S)

Combinational Logic

begin

OUTX <= not s; -- output

end process;

process (CLOCK, RESET)

Sequential Logic

begin

if RESET = '1' then s \ll 0';

elsif rising edge (CLOCK) then

s <= not (INX and s); -- feedback

end if;

end process;

```

### **Mealy Machine**

Mealy Machine: outputs depend on state and inputs. architecture mealy arch of fsm is signal s: bit; -- internal state begin process (INX, s) **Combinational Logic** begin OUTX <= (INX or s); -- output end process; process (CLOCK, RESET) Sequential Logic begin if RESET = '1' then  $s \ll 0'$ ; elsif rising edge (CLOCK) then s <= not (INX and s); -- feedback end if; end process; end mealy arch;

# FSM Example 1) Up/Down Counter

61

• Up/Down Counters: Generate a sequence of counting patterns according to the clock and inputs.

```

entity counter is

port(CLK: in std_logic;

RESET: in std_logic;

COUNT: out std_logic_vector(3 downto 0));

end counter;

architecture counter_arch of counter is

signal s: std_logic_vector(3 downto 0); -- internal state

begin

```

```

COUNT <= s; -- output Combinational Logic

process(CLK, RESET)

begin

if(RESET = '1') then s <= "0000";

else

if( rising_edge(CLK) ) then

s <= std_logic_vector(unsigned(s) + 1); -- feedback

end if;

end if;

end process;

end counter arch;</pre>

```

# FSM Example 1) Up/Down Counter (2/2)

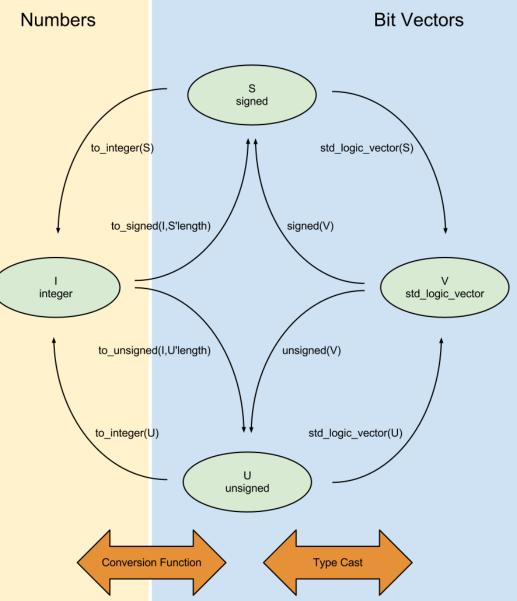

- VHDL is stronglytyped language.

- Data objects of <u>different base types</u>

CANNOT to assigned to each other without using type-casting or type-conversion.

- Type-casting: Move between std\_logic\_vector and signed/unsigned.

- Type-conversion: Move between signed/unsigned and integer.

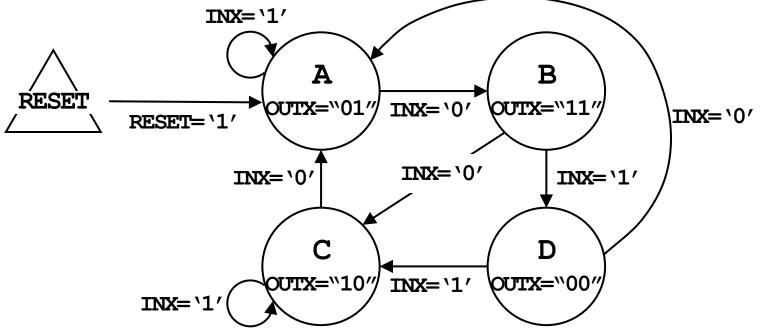

## FSM Example 2) Pattern Generator (1/3)

- Pattern Generator: Generates any pattern we want.

- Example: the control unit of a CPU, traffic light, etc.

- Given the following machine of 4 states: **A**, **B**, **C** and **D**.

- The machine has an asynchronous **RESET**, a clock signal **CLK** and a 1-bit synchronous input signal **INX**.

- The machine also has a 2-bit output signal **OUTX**.

### FSM Example 2) Pattern Generator (2/3)

```

library IEEE;

use IEEE.std logic 1164.all;

entity pat gen is port(

RESET, CLOCK, INX: in STD LOGIC;

OUTX: out STD LOGIC VECTOR (1 downto 0));

end pat gen;

architecture arch of pat gen is

type state type is (A,B,C,D);

signal s: state type; -- state

begin

process (CLOCK, RESET) Sequential

begin

Logic

if RESET = '1' then

s <= A;

elsif rising edge (CLOCK) then

-- feedback

case s is

when A \Rightarrow

if INX = '1' then s \leq A;

else s <= B; end if;

```

```

when B \Rightarrow

if INX = '1' then s \leq D;

else s <= C; end if;

when C =>

if INX = '1' then s \leq C;

else s <= A; end if;

when D \Rightarrow

if INX = '1' then s \leq C;

else s <= A; end if;

end case;

end if;

end process;

process(s)

Combinational

begin

Logic

case s is

when A \implies OUTX \iff "01";

when B \implies OUTX \iff "11";

when C \implies OUTX \iff "10";

when D \implies OUTX \iff "00";

end case;

end process;

end arch;

```

### FSM Example 2) Pattern Generator (3/3)

- Encoding methods for representing patterns/states:

- **Binary Encoding**: Using N flip-flops to represent **2**<sup>N</sup> states.

- Less flip-flops but more combinational logics

- One-hot Encoding: Using N flip-flops for <u>N</u> states.

- More flip-flops but less combination logic

- Xilinx default seeting is one-hot encoding.

- Change at synthesis → options

- http://www.xilinx.com/itp/xilinx4/data/docs/sim/vtex9.html

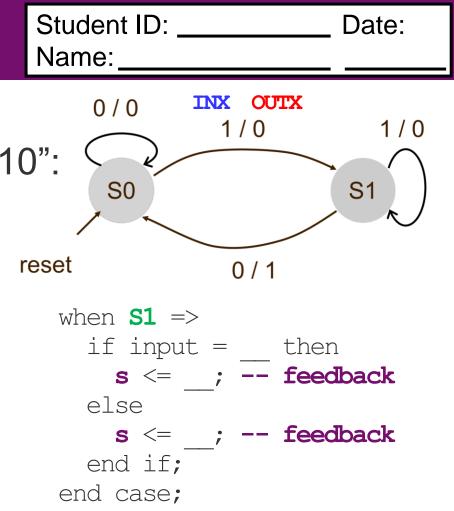

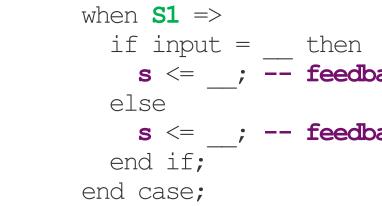

#### **Class Exercise 4.8**

Complete a Mealy Machine that recognizes sequence "10": architecture arch of mealy fsm is type state type is (S0, S1); signal s: std logic; -- state

begin process (CLK, RESET) -- seq begin

```

if (RESET = '1') then s <= ;

else

```

```

if (rising edge (CLK)) then

case s is

when SO =>

```

if input = then s <= ; -- feedback end process;</pre> else s <= ; -- feedback end if;

end if;

end if;

OUTX <= when (s = and INX = )else ; -- output

# **Rule of Thumb: VHDL Coding Tips**

- ① Maintain the internal state(s) explicitly

- **②** Separate combinational and sequential logics

- Write <u>at least</u> two processes: one for <u>combinational logic</u>, and the other for <u>sequential logic</u>

- Maintain the internal state(s) using a sequential process

- Drive the output(s) using a combination process

- **③ Keep every process as simple as possible**

- Partition a large process into multiple small ones

- ④ Put every signal (that your process must be sensitive to its changes) in the sensitivity list.

- **S** Avoid assigning a signal from multi-processes

- It may cause the "multi-driven" issue.

## Summary

- Combinational Circuit and Sequential Circuit

- Combinational Circuit: No Memory

- Decoder

- Multiplexer

- Bi-directional Bus

- Sequential Circuit: Has Memory

- Latch

- Flip-flop

- Asynchronous Reset and Synchronous Reset

- Finite State Machine (FSM)

- Clock Edge Detection

- Direct Feedback Path

- Types and Examples